高密度実装技術High-Density Packaging Technology

高密度実装技術に関するお問い合わせ今後、Mobile、Automotive、HPC(ハイパフォーマンス・コンピューティング) 、IoT、Serverといった用途のために高機能デバイスの需要がさらに増加します。これらのデバイスでは、求められる機能に応じての様々な構造、例えばチップレットなどの最先端デバイス性能を向上させるために、パッケージ技術が注目されています。

中でもスマートフォンやタブレットPCなどモバイル端末の普及に伴い、ICチップやパッケージ基板の薄型化・高密度化のニーズが高まるとともに、ウェハーレベルパッケージ(WLP:Wafer Level Packaging)が重要な実装技術とされています。

一方、ハイエンドサーバでは大きなチップサイズに対応するため、基板も大型である必要があります。

このように、モバイルデバイスからサーバまで幅広い分野の高密度実装技術に対応するため、パッケージング基板のビルドアップ配線形成に半導体微細化技術を導入する検討が進められており、パネルレベルパッケージ(PLP:Panel Level Packaging)が新たな実装技術として注目されています。

特にパッケージング基板は、510mm×515mmあるいはそれ以上の大きな四角基板(パネル)で構成されています。そのため、反りや耐熱性、機械的特性に加え、多様なパネルのハンドリングといった課題があり、これは従来のシリコンウェハー工程とは異なる特有の課題です。

ULVACでは、WLPやPLP向けの製造プロセスにおいて、スパッタリング、エッチング、デスカム装置、デスミア装置などの技術を提供しています。

INDEX

WLP・PLPなどの先端実装に使われるULVAC製品ラインナップ

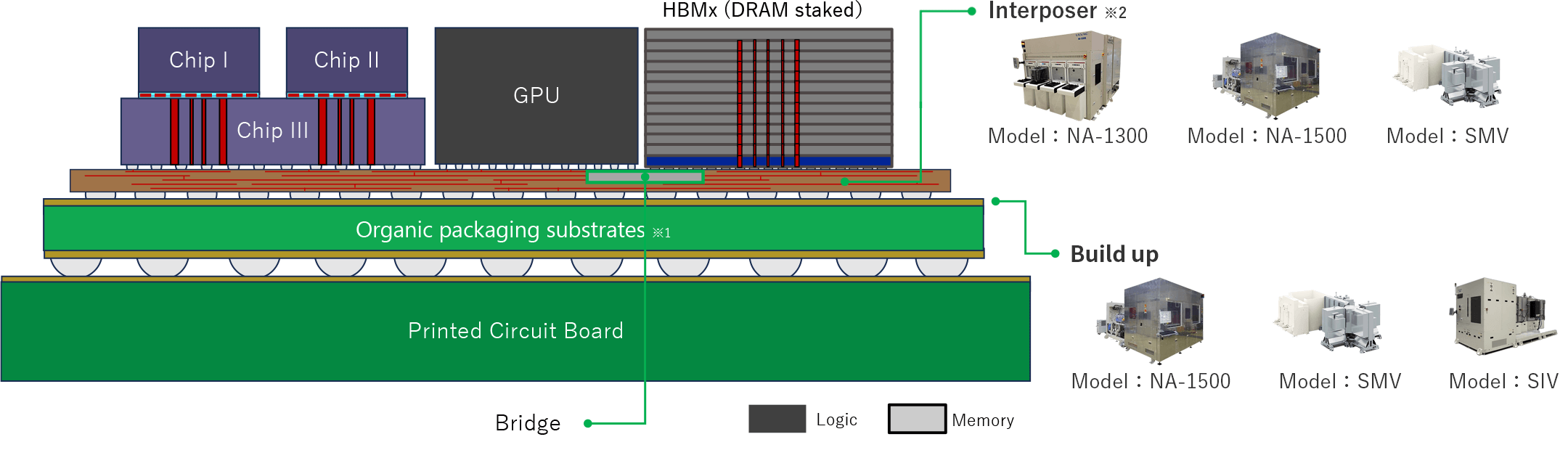

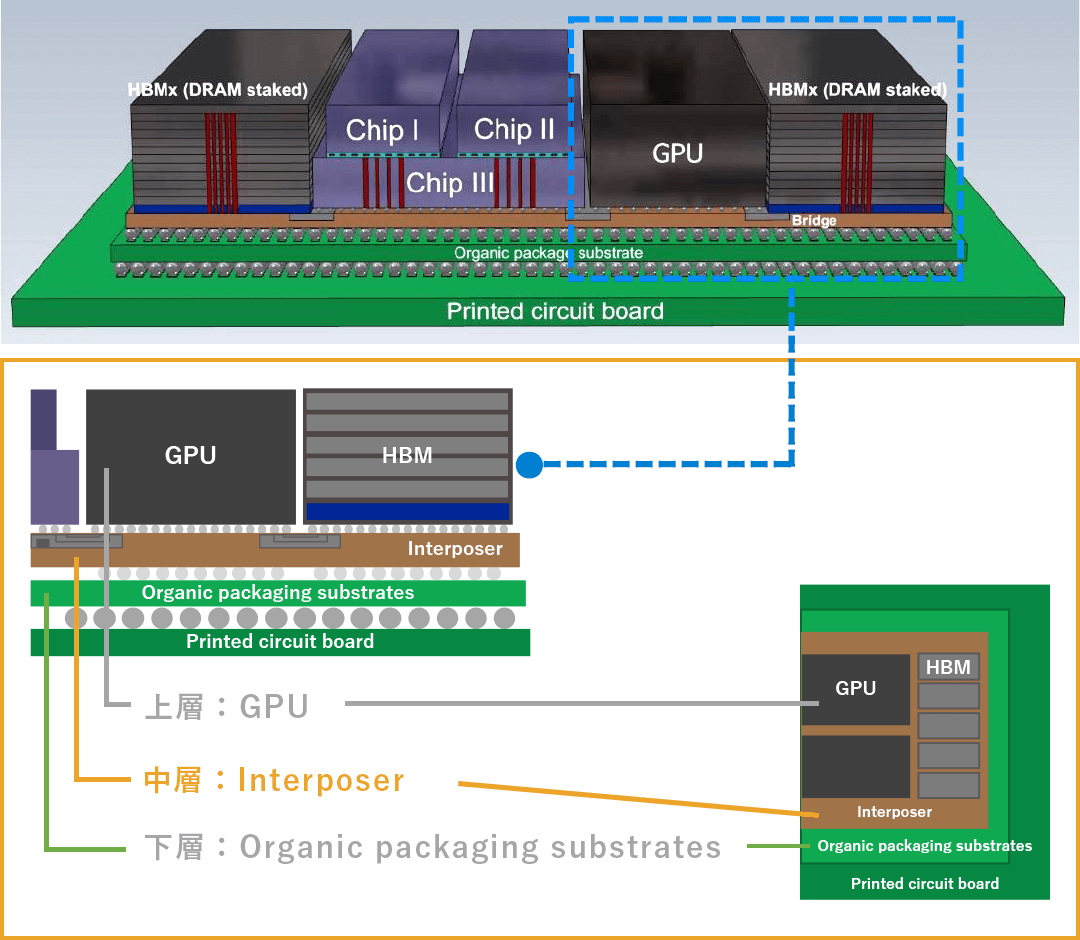

※1:当サイト内ではこの箇所をPackage substrateとする

※2:当サイト内ではこの箇所をInterposerとする

デバイス構造の一例を考えると、複数のデバイスが基板の上に搭載されていますが、新しい機能や効率化などのために先端のデバイス同士や先端と従来のデバイスを混在させて接続することを目的として、様々な材料や構造がパッケージング全体で日々検討されています。

デバイス構造や材料に対応する課題はそれぞれの構造毎、材料毎に産まれており適切に対応する処理装置や方法が検討されています。

アルバックでは、それぞれの課題に適切に対応するような装置をラインナップしています。

PLPパッケージング基板向け 課題と対応装置

チップや、チップを搭載したRDL(Redistribution Layer)とマザーボードを接続するためのパッケージング基板は、周辺テクノロジーの進化に伴い、技術要求がますます高度化しています。

市場を支える高い生産性や信頼性を維持しつつ、次世代に向けた加工方法の変更が検討されています。

配線形成工程では、ドライデスミアやスパッタリングシードなどのドライプロセス技術が導入され始めています。用途や使用環境に応じて様々な構造が存在し、高性能化を支えるための材料開発も活発に行われています。

アルバックでは、材料や表面状態など、それぞれの課題に適切に対応する装置をラインナップし、技術革新を支援しています。

プロセスフロー

① ラミネーション

② レーザードリル③ デスミア

④ シード層形成

⑤ DFRラミネーション

⑥ DFR露光・現像⑦ デスカム

⑧ Cu電解めっき

⑨ レジスト・メタル除去

- ③ デスミア工程における側面および底面の平滑化の課題

- Via(ビア)底にスミア(Smear)残渣とフィラー由来の凹凸

- 次工程でのCuとの密着性低下や配線の抵抗成分の増加

- ④ 平滑表面への高密着成膜の課題

- 微細化トレンドへの対応、表面平滑なVia(ビア)とのシード膜の密着性の維持が困難

- ⑦ デスカム工程における側面および底面の平滑化の課題

- Via(ビア)底にスミア(Smear)残渣とフィラー由来の凹凸

- 次工程でのCuとの密着性低下や配線の抵抗成分の増加

PLPパッケージング基板向けデスミア工程における課題とソリューション

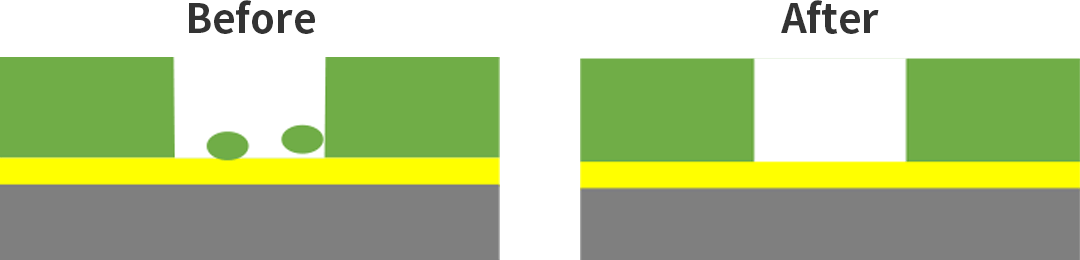

- 課題デスミア工程における側面および底面の平滑化

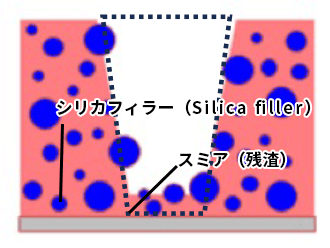

各絶縁膜層を上下で繋ぐVia(ビア)の形成はCO2・UVなどの レーザードリルが用いられ、Via形成後、Via底には「スミア:Smear」と呼ぶ残渣とフィラー由来の凹凸を残ることが多く、次工程に進んだ場合、Cu との密着性低下や配線の抵抗成分の増加等、配線信頼性低下に繋がるため、スミア除去のための「デスミア(Desmear)」工程が不可欠になります。

- 解決プラズマエッチング技術を用いたドライデスミア

-

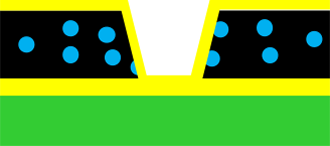

処理前

Via(ビア)底にスミア(Smear)残渣とフィラー由来の凹凸が残っている状態

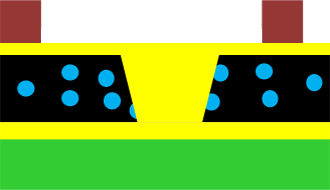

処理後

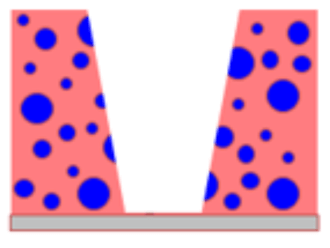

スミア除去時にVia(ビア)側壁のシリカフィラーの凹凸も同時にスムージングすることが可能

ドライプロセスであるプラズマエッチングは、ウエットプロセスに比べ、各プラズマ条件(ガス比やその他パラメータ)を材質や形状毎に残渣除去と表面粗さを最適化することができます。

PLPパッケージング基板向けシードCuにおける課題とソリューション

- 課題平滑表面への高密着成膜

従来のパッケージング基板のCu配線層形成は無電解メッキ法が用いられてきましたが、パターンの微細化や表面の平滑性が上がることにより、Cu配線層と下地層の密着性の維持が難しくなりました。

- 解決次世代Cu配線形成へのスパッタリング応用

スパッタリングを用いたシード層成膜によって、下地膜との十分な密着性を得ることができます。

アルバックでは、510㎜×515㎜以上のサイズのパネル基板上に均一に成膜できます。

インターポーザ製作工程での課題とソリューション

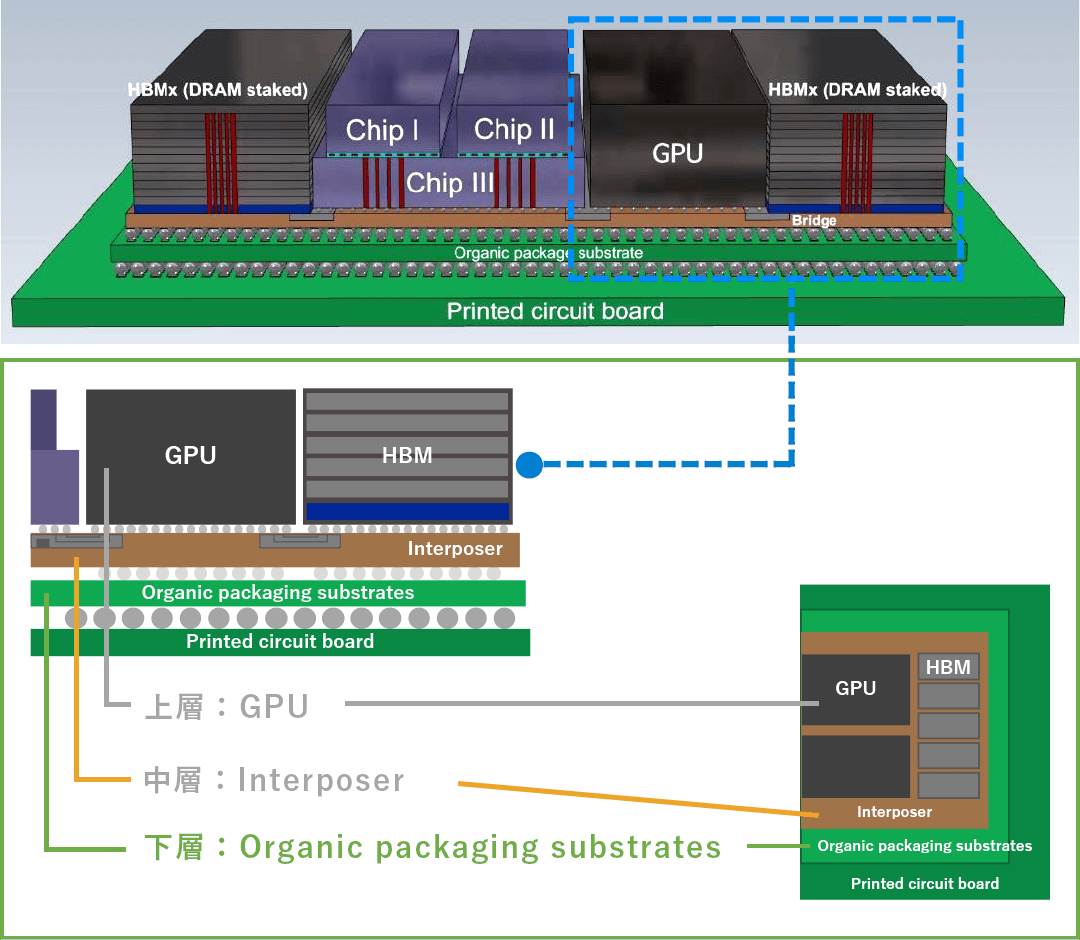

デバイス構造の一例として、複数のデバイスが基板上に搭載されるケースを考えることができます。

先端技術を用いたデバイスだけでなく、成熟した世代のデバイスを再利用することで、その活用性を高める取り組みが進められています。これらの異なる世代のデバイスを混在させて接続することで、新しい機能の実現や効率化を図り、市場の要求に迅速に対応することが目的です。

このような目的を達成するために、パッケージング全体では様々な材料や構造が日々検討されています。デバイス構造や使用される材料に応じた課題は、それぞれの構造や材料ごとに異なり、適切な処理装置や方法が求められます。

アルバックでは、これらの課題に対応するための装置を幅広くラインナップし、最適なソリューションを提供しています。

Via製作工程

① PI塗布

② 露光現像③ デスカム

④ シード層形成

⑤ 電解めっき

配線 製作工程

① シード層形成

② PR塗布

③ 露光現像④ デスカム

⑤ 電解めっき

⑥ レジスト除去

⑦ シード層除去

- スカム除去とfooting除去

- 高アスペクト比Via(ビア)底辺にあるスカムおよびfooting除去を取りきるのは難しい。

“Model:NA-1300/1500” による課題解決へ

アッシング装置Model:NA-1300

アッシング・エッチング装置Model:NA-1500

プラズマ技術を用いたドライデスカム応用

- 課題スカム除去とfooting除去

高アスペクト比Via(ビア)底辺にあるスカムおよびfooting除去を取りきるのは難しい。

- 解決アッシングによる下地残渣の除去

当社のデスカム装置は、微細化された加工工程の中で樹脂向けの優しい処理をマイクロ波プラズマ技術と平行平板プラズマ技術を組み合わせた独自構成により達成したことで、高アスペクト比であってもアッシングでFootingの除去が可能になりました。

・形状を保持しながら残渣を除去

・高アスペクト比Viaに対するFooting除去その他の用途:腐食の防止・親水性・粗さの制御