メモリ・ロジックMemory and Logic Solutions

メモリ・ロジック製造装置に関するお問い合わせ半導体デバイス構造の進化に伴い、微細化や低抵抗化、応力制御が重要課題となっています。

アルバックはこれらの技術課題をお客様とともに解決し、お客様の最終製品を通してより高性能な半導体デバイスを社会に送り出すことに貢献しています。特に、アルバックの得意分野である成膜技術においては、最先端であるオングストローム世代の半導体デバイス開発、量産にも採用されています。

INDEX

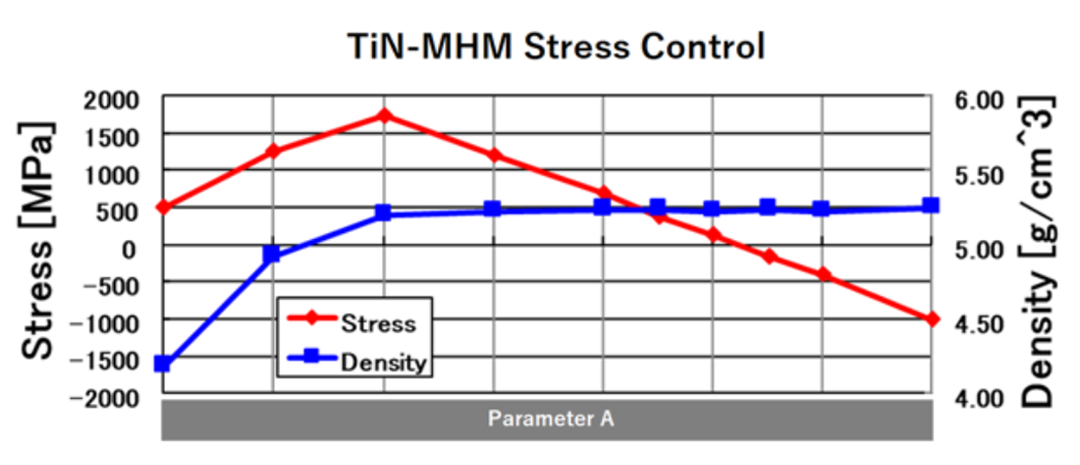

自在な応力制御を可能にしたメタルハードマスク成膜プロセス

先端半導体デバイス製造工程においては、エッチングによる高精度のパターン転写を可能にするメタルハードマスク(MHM)が採用されています。

アルバックは、お客様の高度な技術ニーズに応えるべく、十分な膜密度を維持したまま応力を自在に制御できるTiNメタルハードマスクプロセスを早期に市場投入し、先端から成熟ロジックデバイス量産まで、幅広いお客様に標準装置として認定いただいています。

また、タングステンやシリコン等のマスク材料成膜も開発し、これらの材料を使用したハードマスクプロセスの量産工程への導入が始まっています。

アルバックModel:ENTRONのTiNメタルハードマスクプロセスの特徴

- 高密度TiN膜の自在な応力制御(グラフ参照)

- 最先端ロジック半導体製造に対応するパーティクル制御

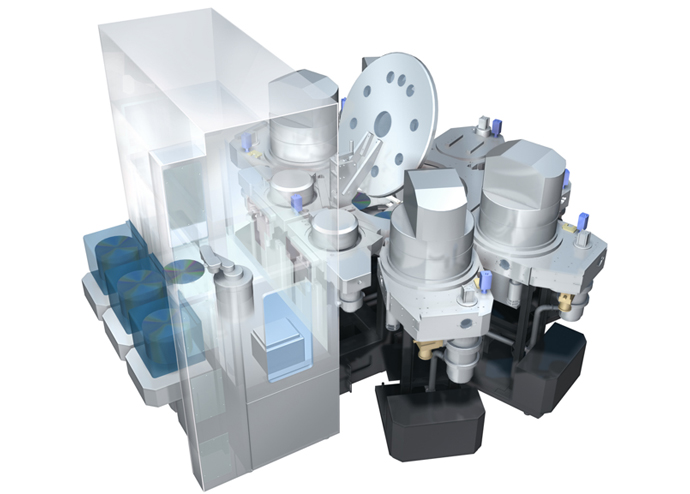

微細化が進むデバイス製造において、パーティクルの管理は重要です。アルバックの”Model:ENTRON”は、搭載されるモジュールが持つパーティクル抑制機能を使用することで低パーティクルを実現します。

- 省スペースを実現するSingle Core Type

※チャンバ構成はご要求プロセスによって異なります。

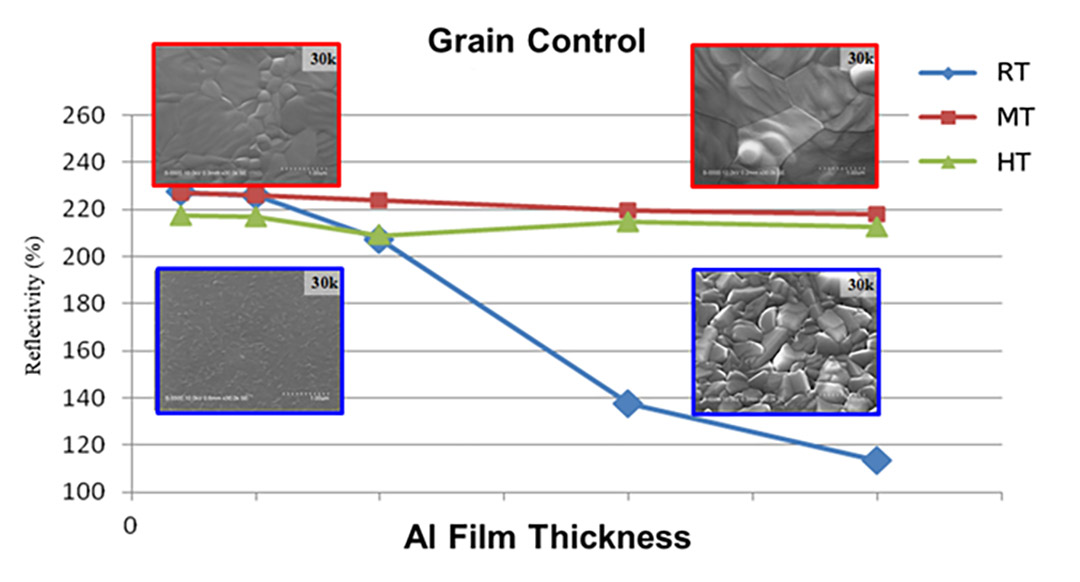

高い量産性を実現するハイレート対応の厚膜アルミニウム配線成膜プロセス

厚膜アルミニウム配線成膜プロセスは、半導体製造工程において様々な配線用途に採用されており、引き続き重要な役割を果たしています。

アルバックは、厚膜アルミニウム配線成膜プロセスにおける重要な要素である温度コントロール、ハイレート、パターンへの高い埋め込み性を実現しており、モバイル用メモリデバイスの再配線アルミニウム成膜工程において、多くのお客様の量産工場にて採用されています。

アルバックModel:ENTRONの厚膜アルミニウム配線成膜プロセスの特徴

- チャンバ内部の温度上昇を防ぐ冷却性能を備えたモジュール設計

- 成膜時の基板温度をコントロールし、安定した膜質を達成(左グラフ参照)

- Pad工程・再配線工程、メタル配線工程に適用可能な埋め込み性能(右図参照)

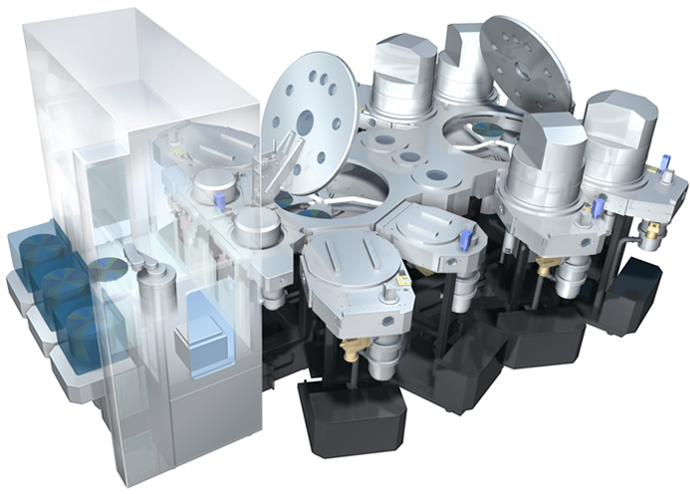

高い生産性と信頼性を有するCuシード配線成膜プロセス

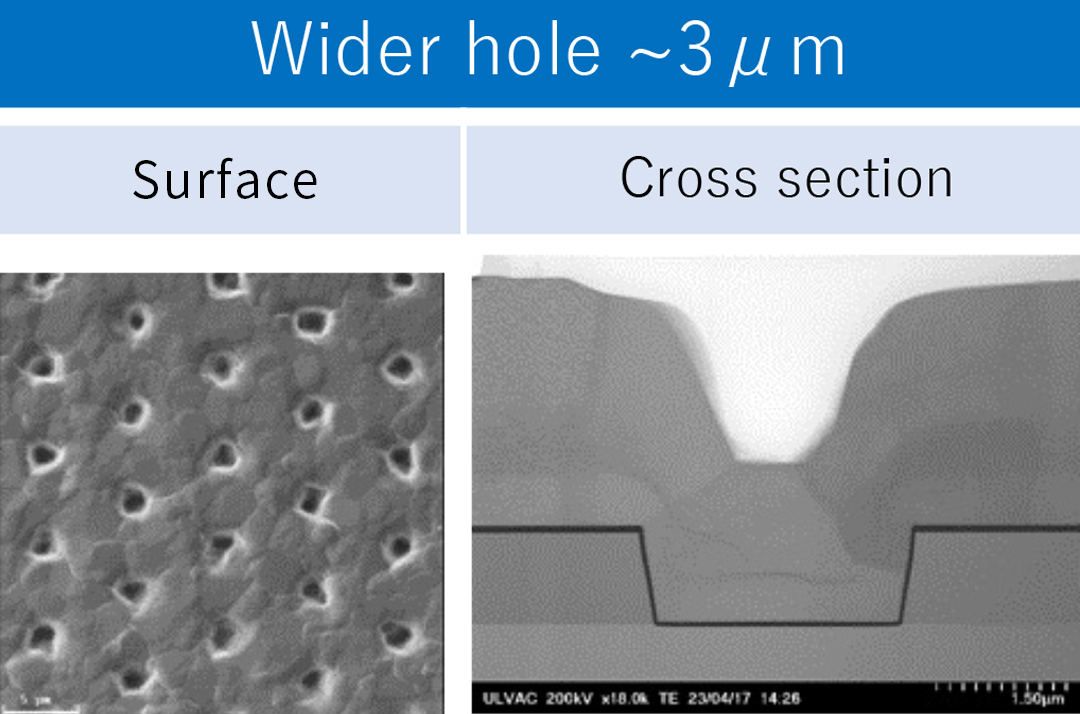

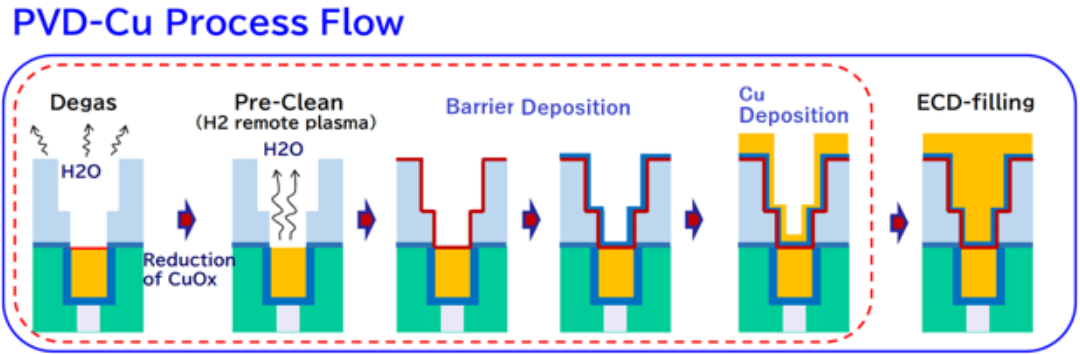

半導体製造工程におけるCu(銅)シード配線プロセスは、半導体デバイスの微細化に伴うRC遅延、EM耐性、絶縁膜の性能向上といった課題に対応するため、バリア層やLow-k材料の改良、埋め込みプロセスの最適化、新材料の採用など、多岐にわたる技術革新が進んでいます。

アルバックは、他社に先駆けCuのセルフイオナイズドスパッタ(Self-Ionized Sputter, SIS)を採用し、微細化に対応してきました。

アルバックModel:ENTRONのCuシード配線成膜プロセスの特徴

- 高スループット

Tandem Core Typeで90wph(wafer per hour)を実現

※実際のスループットはご要求プロセスによって異なります。 - 低パーティクル/良好な膜厚均一性

最新のアルバックの半導体製造装置

強化されたデータ収集・解析による歩留まり改善と予防保全

アルバックの最新機種“Model:ENTRON-EXX”は、優れたデータ収集・解析能力を備え、お客様の量産工場における予防保全、歩留まり・量産性の維持、改善に貢献します。またモジュール交換/追加を素早く行える柔軟性によってお客様の開発スピード改善にも寄与します。

そして、アルバックの半導体製造装置は、アルミニウム、Cu(銅)、タングステン、タンタル等の金属膜だけでなく、AlOx(酸化アルミニウム)、AlN(窒化アルミニウム)等の絶縁膜の実績もあります。更に、ウェハレベルパッケージの成膜として再配線層、シリコン貫通電極およびバンプ下地のバリア/シード層の成膜も可能です。