MEMS製造装置Micro Electro Mechanical Systems Solution

MEMS製造装置に関するお問い合わせ近年、MEMSデバイス技術はますます進化しており、自動運転や次世代ウェアラブル端末(スマートグラス等)、各種センサー、アクチュエータに不可欠な存在となっています。

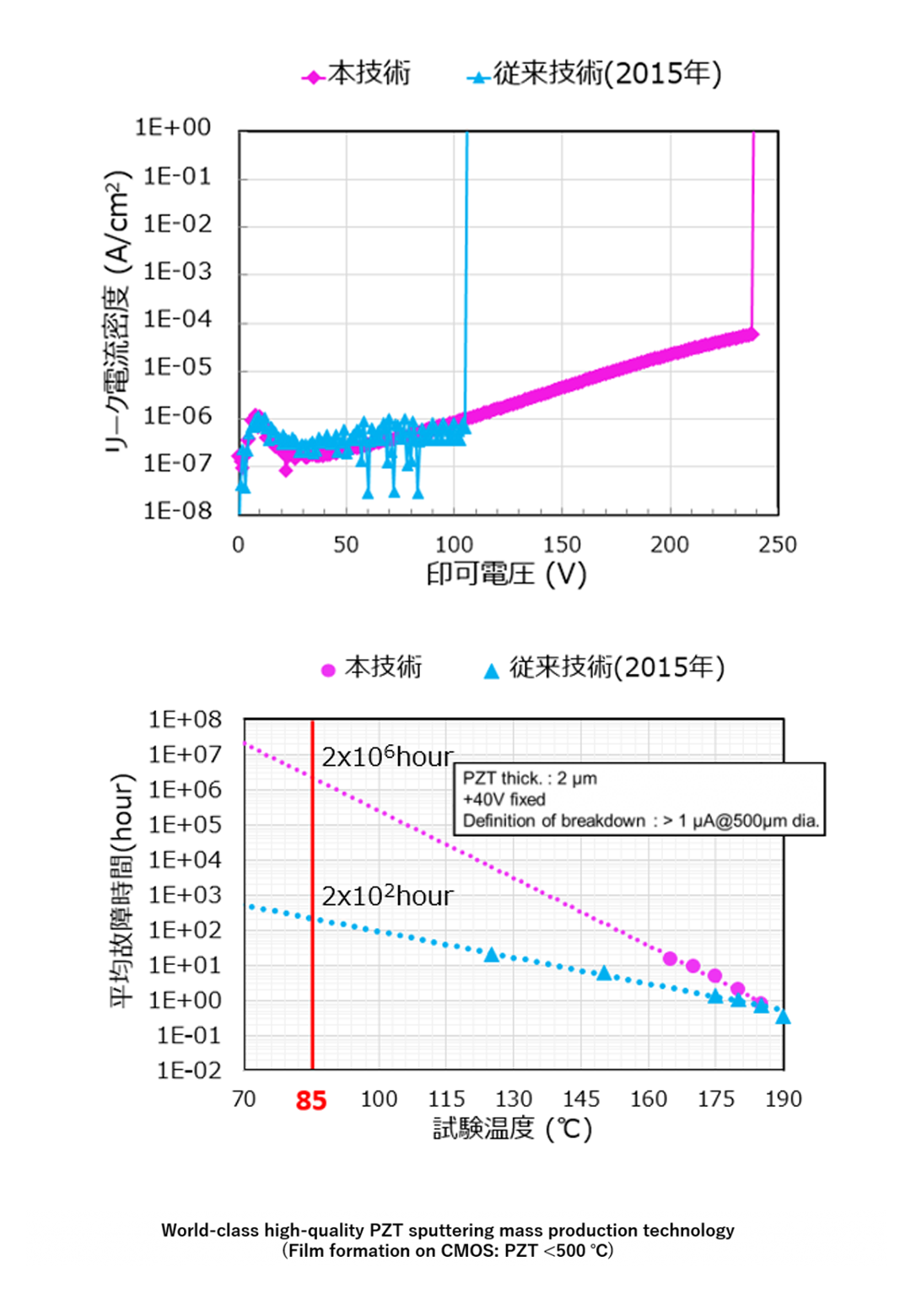

MEMSデバイス開発における障壁となっていた技術課題を解決するため、PZT圧電薄膜のスパッタリング量産技術の高度化を実現しました。従来一般的であった塗布法(ゾルゲル法、Sol-Gel)では低温プロセスでの形成が不可能でしたが、アルバックは2015年にPZT圧電薄膜を低温スパッタリングプロセスで形成する世界最高レベルの技術を確立し、次世代MEMS技術としてさらなる開発を進めています。

また、独自技術をさらに進化させることで、デバイスの実用化に求められる信頼性を大幅に向上させ、さらに装置運用の最適化を行うことでランニングコストの改善などを同時に満たし、世界最高水準の量産技術を実現します。

INDEX

圧電MEMSの製造工程における課題と対応装置

圧電MEMSの製造工程

① 圧電素子の形成

② 上部電極Pt/PZTエッチング

③ 下部電極Ptエッチング

④ 保護膜の形成

⑤ 電極部分の引き出し

⑥ 中空構造の形成

- ① 圧電MEMS製造工程における圧電素子形成の課題

- 500℃以下の低温プロセス

- 高い圧電性能と信頼性の両立

- 量産化に向けた高スループットと高い再現性

- ② 圧電MEMS製造工程における上部電極Pt/PZTエッチングの課題

- パターン側壁への付着

- 下部電極との選択比

- 安定した生産

圧電MEMS、CMOS搭載を可能にする低温スパッタリングプロセスのご提案

- 課題圧電MEMS製造工程における圧電素子形成の課題

-

- 500℃以下の低温プロセス

圧電MEMSをCMOSへ搭載するには500℃以下の低温プロセスでなければなりません。しかし通常PZTの結晶化にはスパッタリング法で600℃必要になります。

- 高い圧電性能と信頼性の両立

- 量産化に向けた高スループットと高い再現性

- 500℃以下の低温プロセス

- 解決

-

- バッファ層の活用

バッファ層を活用し、500℃以下でのPZTの結晶化を実現します。

- PZTスパッタ向けのハードウェア

500℃以下の低温プロセスでありながら優れた圧電性能と高信頼性を両立します。

- 同一装置内でPZT構成を実現

クラスター式スパッタリング装置のため各積層構造を同一装置内で成膜します。

ハイクオリティのPZTスパッタ膜を安定成膜

・CMOS上成膜対応

・PZT低成膜温度 “Model:SME-200” 装置詳細ページへ

“Model:SME-200” 装置詳細ページへPiezo-MEMS量産用スパッタリング装置Model:SME-200

マルチチャンバー搭載で、PZT full stack(上下電極+PZT)を一貫成膜可能です。

- バッファ層の活用

圧電MEMSに最適化されたエッチングプロセスのご提案下部電極であるPtとの高い選択性・側壁への付着低減を実現

- 課題 圧電MEMS製造工程における上部電極Pt/PZTエッチングの課題

-

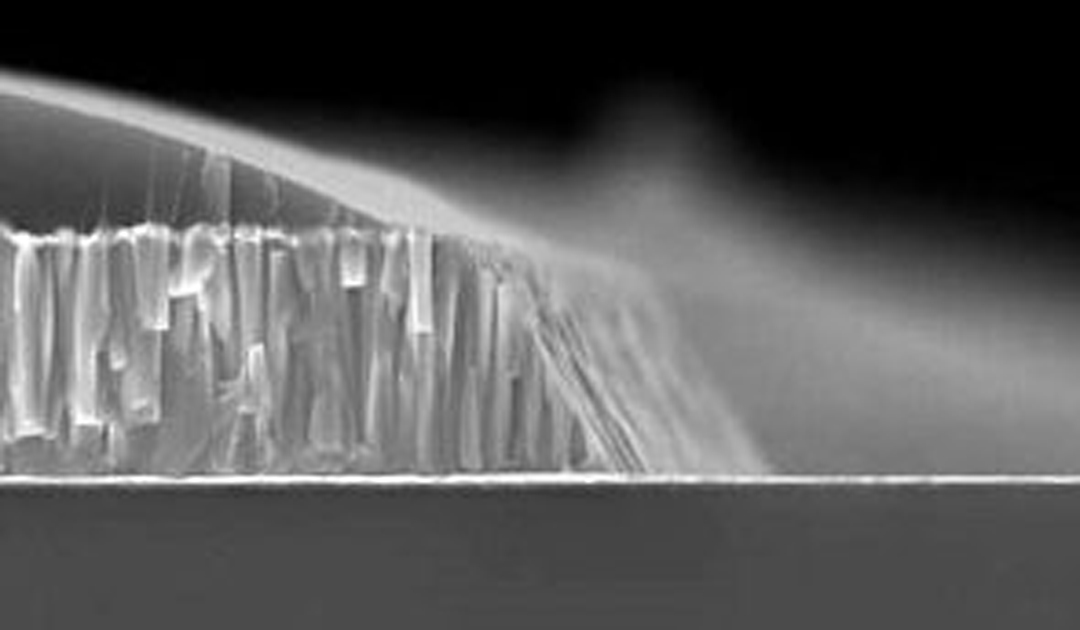

- パターン側壁への付着

難エッチング材料のため、エッチング生成物が側壁に付着しやすくなります。

- 下部電極との選択比

膜構成が数μmのPZT膜と約100nmの金属電極で構成されていて、下部電極を残す8インチプロセスが困難です。

- 安定した生産

EPD信号の低下などにより安定した生産が困難です。

- パターン側壁への付着

- 解決

-

- PZT多層膜専用のプラズマソース活用

エッチング分布3%以下を達成します。側壁デポがなく、PZT/Ptの選択比>5@8inchウェハー(>10@6inchウェハー)対応可能です。

- 高均一性と精密な終点検出により、各エッチング膜下部の層の掘れ量を最小化

下地の掘れ量を最小化する高均一性(<+/-3%@8inch)と精密な終点検出を提供します。

- EPD信号の低下やエッチングレートの低下のないハードで安定生産が可能

6-8インチで安定した生産が可能です。

下部電極であるPtとの高い選択性を持つPt/PZTエッチングプロセスを提供します。(選択比例: PZT/ Pt >5@8inch, >10@6inch) - PZT多層膜専用のプラズマソース活用